SRAM databook

high-speed, high-density monolithic SRAMs

inova microelectronics corporation

first edition august 1990

#### How To Use The Inova Databook

The Inova Databook has been designed to briefly introduce you to Inova, to familiarize you with our products, to provide you detailed specifications on our products, and to assist you in ordering the products that best suit your specific design requirements. The common thread throughout this effort has been YOU, our customers.

If you are unfamiliar with our company, a brief overview of our corporation is found on page 4.

If you would like to glance at the types of products Inova manufactures, please refer to the Product Selector Guide on page 11.

If you are trying to replace one or more of our competitors' parts with one of our high density monolithic devices, you may find the competitive device listed in our Cross Reference Section on page 17.

Once you have determined the correct device to use, the Product Data Section of the book will enable you to design it into your system correctly. Electrical and timing information is contained in this section, and the Packaging section at the rear of the book contains dimensions on all the packages we offer in our product line.

Memory Scale, a new memory performance comparison factor which is defined as the total number of memory bits divided by the device access time, is included for each Inova device. We encourage you to compare the Memory Scale number of competitive memory products with Inova memories.

A Quality and Reliability section outlines the system of controls we maintain to provide you with the highest quality and most reliable products and services. This section is found on page 21.

Several Application Notes on using Inova products are in the back of the book. These may help you consider different alternatives in your design with Inova devices.

Ordering information is included at the end of each individual data sheet and on pages 9 and 150.

Inova has the talent and the products to help you design superior advanced electronic systems that will help keep you a step ahead of your competitors. We look forward to hearing from you.

Inova Microelectronics Corporation designs, produces and markets high density, high speed memory and special purpose semiconductor devices. Our headquarters in Santa Clara, California is augmented by our research and development and marketing group located in Colorado Springs, Colorado.

Inova has developed Inroute™, a proprietary technology that enables Inova to economically produce semiconductor devices on relatively large areas of silicon. This technology, when combined with our high speed silicon processing and design talents, has placed and will continue to maintain Inova in the forefront of semiconductor memory technology.

Inova subcontracts its wafer fabrication activities to silicon foundries worldwide to ensure a reliable large volume of manufacturing capacity. Since some of our products have been specified on Standardized Military Drawings which require MIL-STD-883C screening and controls, the rest of our products benefit from this influence.

Inova products include 256K and 1M monolithic memory devices available in a variety of widths, with a 4M monolithic device available soon. A high speed cache memory, a neural network chip and other specialized memory devices are also in the works. Inova will continue to provide semiconductor devices designed to solve industry-wide and customer- unique requirements.

## Letter from the President

Dear Reader.

We would like to thank you for considering **Inova** for your static random access memory needs. It is our objective to make you a satisfied customer by solving your needs with our products and services.

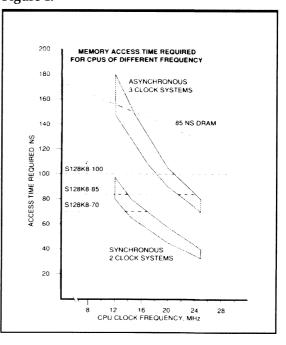

The world's first production-released monolithic 1-Megabit static RAM, the S128K8, was from **Inova**. The S128K8 device has been in production for over two years now, and was the first monolithic 128Kx8 SRAM available on a Standardized Military Drawing. Having established that leadership, we are committed to staying at the forefront of high density memory technology. During 1990, we will continue our pioneering with the introduction of our four and sixteen megabit SRAM's, as well as other highly sophisticated special application memory products.

Although our products are what formally generates revenue to further our business, our people create the products that address your needs as a customer. We would appreciate your feedback on the devices we have designed that appear in this databook. Feel free to contact any of us to obtain more information on our products, or to discuss your particular design challenges and how we might better serve your needs.

We would like to be your memory supplier, and we appreciate the consideration you have given us by reviewing our databook. When you determine the correct **Inova** product to satisfy your needs, contact your local sales representative, distributor, or our Customer Service department to place your order!

Vaemond H. Crane

President

inova

## **Important Notice**

Inova guarantees that its circuits will be free from defects in materials and workmanship under normal use and service when operated under recommended operating conditions, and that these circuits will perform to current specifications in force at the time of their manufacture. Inova backs its devices with the Inova standard warranty which is detailed on the reverse of the Inova sales order acknowledgement. Testing and other quality control techniques are utilized to the extent Inova deems necessary to support this warranty. Unless mandated by specific purchase order terms or required by military specifications, testing of all parameters of each device is not necessarily performed. Inova assumes no responsibility for the use of any circuits described in this databook, and does not convey any license under its patent rights or the rights of others.

The information presented in this databook is accurate to the best of our knowledge. Inova reserves the right to make changes in the device specifications to improve manufacturability, reliability, or performance, or to change the availability of the devices themselves at any time without notice. Inova assumes no responsibility for any errors or ommissions in this book, updates to this databook, or for applications assistance or customer product designs.

Inova products are not authorized for use as critical components in life support devices or systems intended for surgical implant in the body without express written consent of the president of Inova Microelectronics Corporation. Buyer agrees to notify Inova of any such intended end use whereupon Inova shall determine the suitability and availablity of such use.

> © Inova Microelectronics Corporation, 1990 All Rights Reserved

## Table of Contents

| Ordering Information            | 9   |

|---------------------------------|-----|

| Product Selector Guide          | 11  |

| Cross Reference List            | 17  |

| Quality and Reliability         | 21  |

| Product Data and Specifications | 41  |

| Application Notes               | 107 |

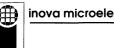

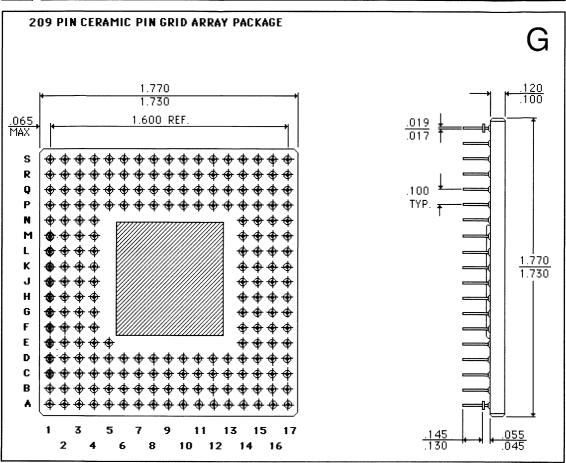

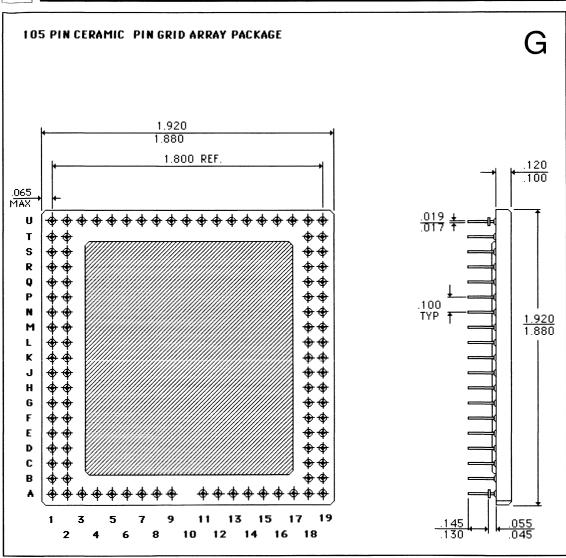

| Packaging                       | 135 |

| Sales Offices                   | 151 |

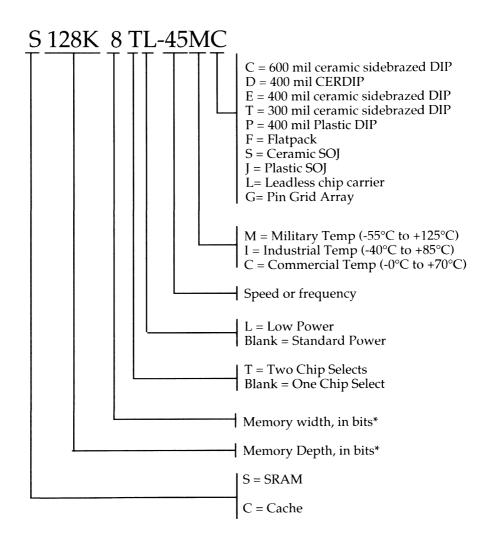

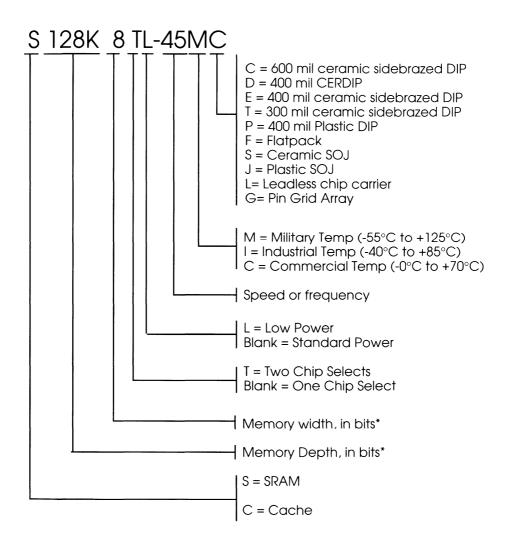

<sup>\*</sup>or another unique circuit designator

| inova microelectro | onics corporation, 2<br>Phone: 408-980- | 2220 Martin Ave<br>0730 Fax: 408- | enue, Santa Cla<br>-980-1805 | ara, CA 95050 |  |

|--------------------|-----------------------------------------|-----------------------------------|------------------------------|---------------|--|

|                    |                                         |                                   |                              |               |  |

|                    |                                         |                                   |                              |               |  |

# **Product Selector Guide**

## Product Selector Guide

# 32K x 8 bit SRAMs

| Inova       | Access Time | Packag | es   | Temp    |              |      |

|-------------|-------------|--------|------|---------|--------------|------|

| Part Number | ns Max      | Type   | Pins | Range   | Comments     | Page |

| S32K8       | 55, 70,     | C, L   | 28   | C, I, M | DESC SMD No. |      |

| _           | 85, 100     |        |      |         | 5962-88662   | 43   |

| S32K8L      | 55, 70,     | C, L   | 28   | C, I, M | DESC SMD No. |      |

|             | 85, 100     |        |      |         | 5962-88552   | 43   |

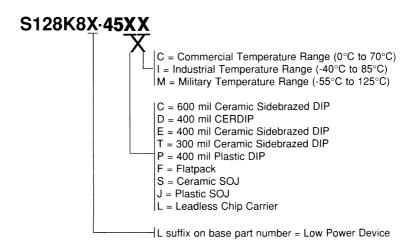

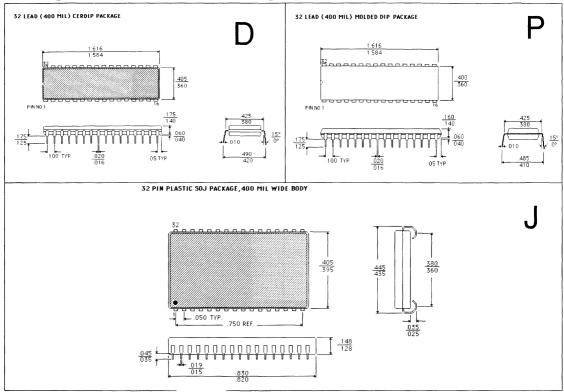

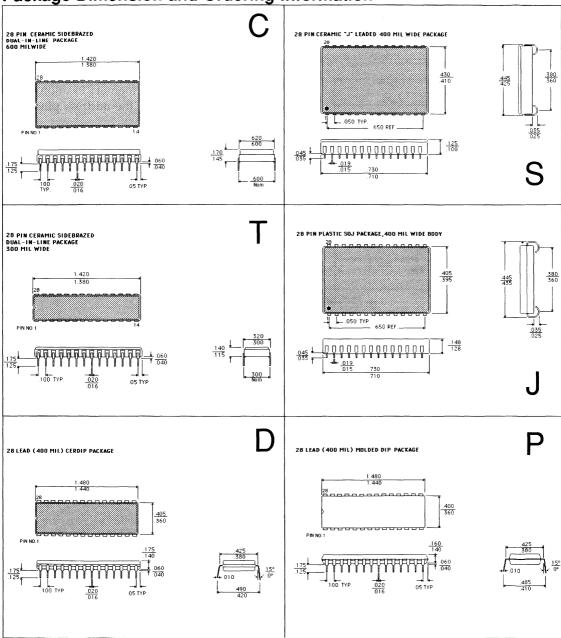

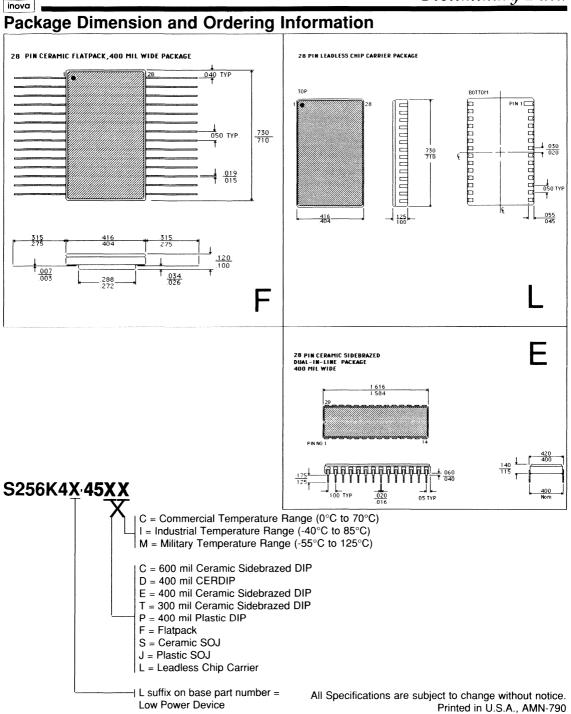

C = Commercial Temperature Range (0°C to 70°C)

I = Industrial Temperature Range (-40°C to 85°C)

M = Military Temperature Range (-55°C to 125°C)

L suffix on base part number = Low Power Device

T suffix on base part number = Two Chip Select Option

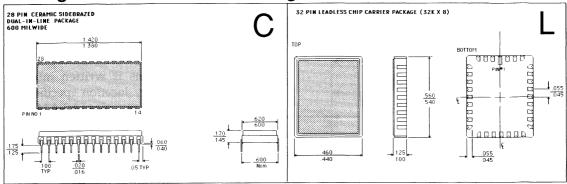

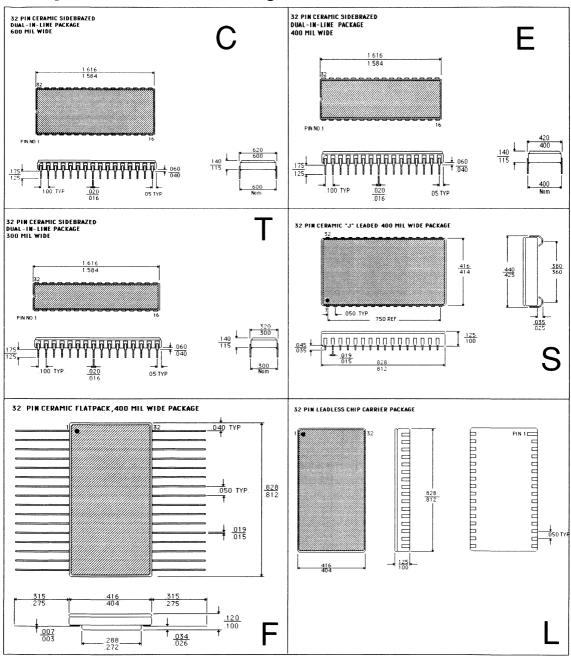

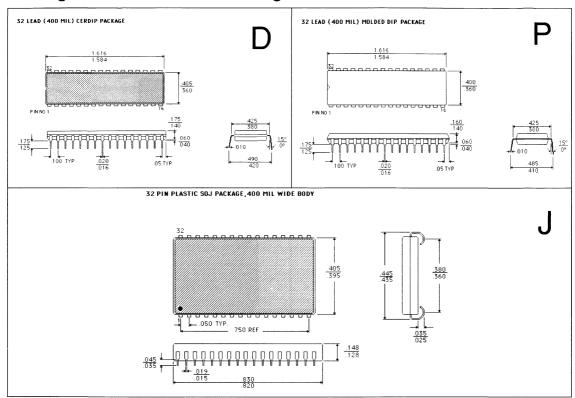

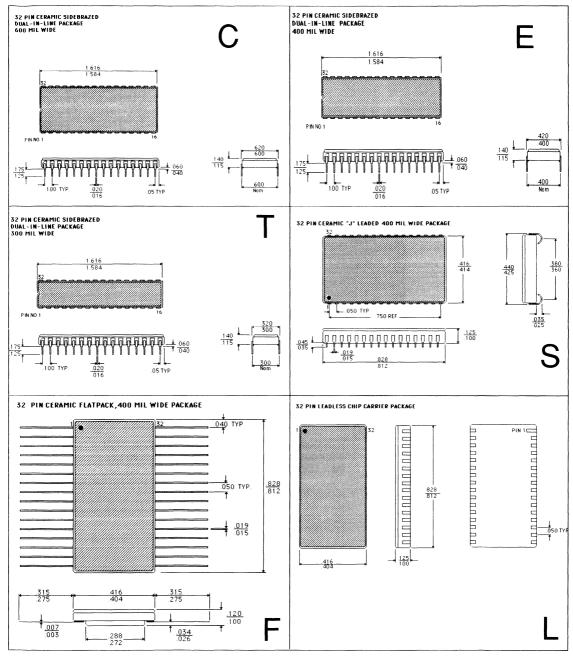

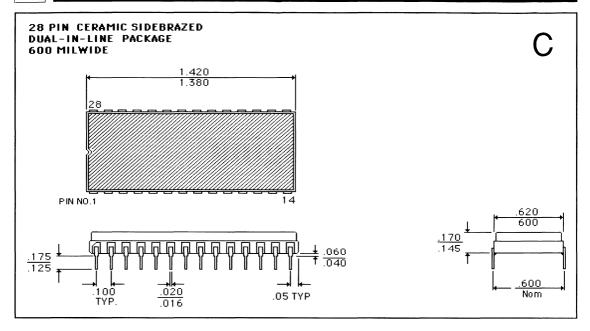

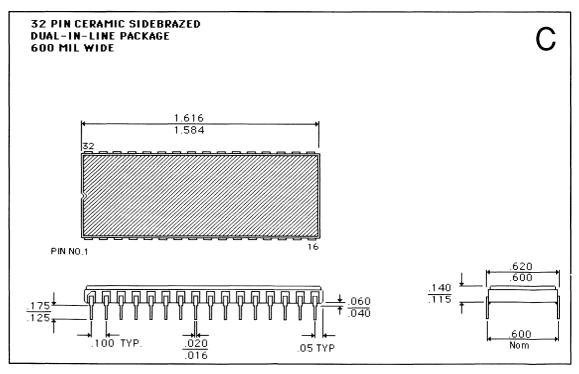

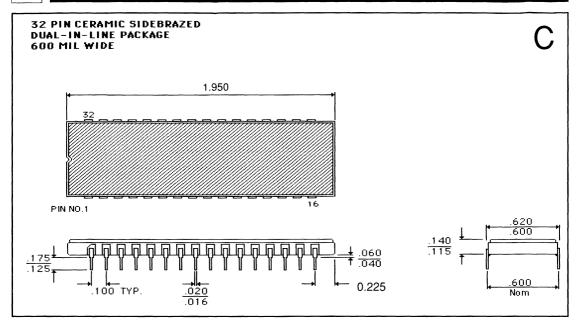

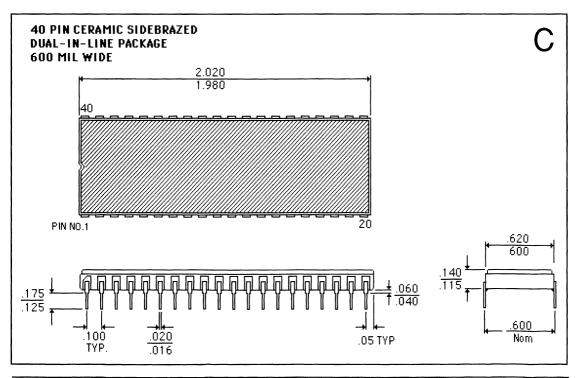

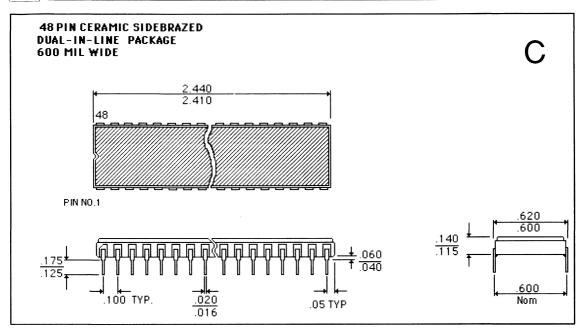

C = 600 mil Ceramic Sidebrazed DIP

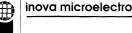

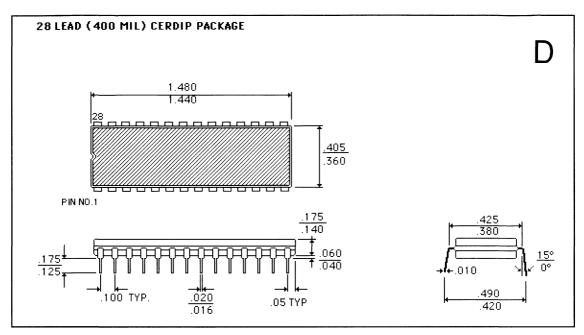

D = 400 mil CERDIP

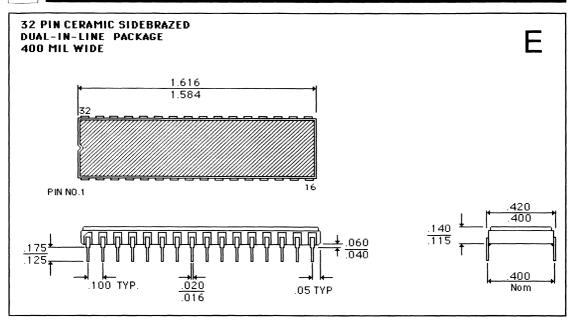

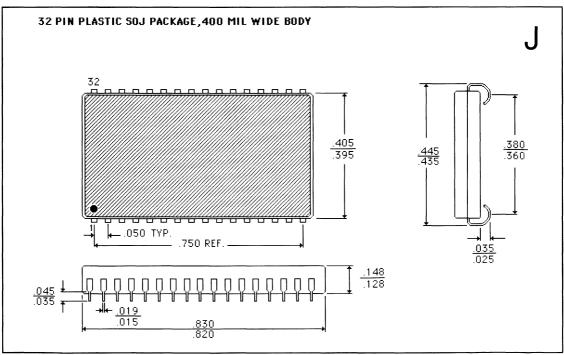

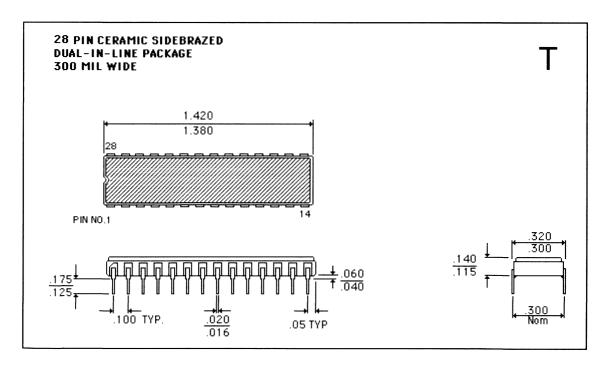

E = 400 mil Ceramic Sidebrazed DIP

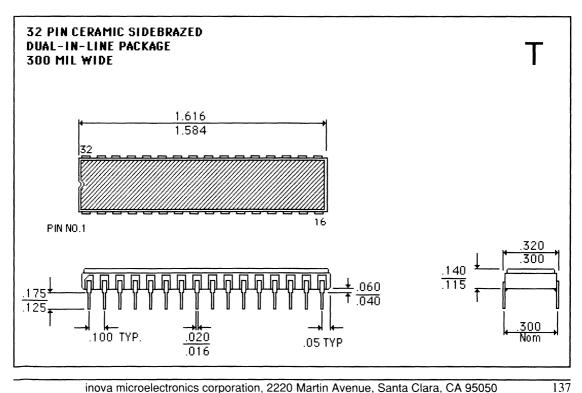

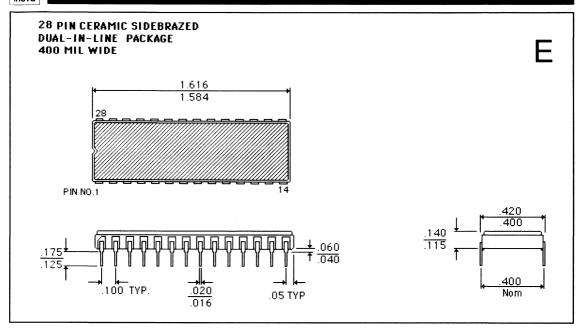

T = 300 mil Ceramic Sidebrazed DIP

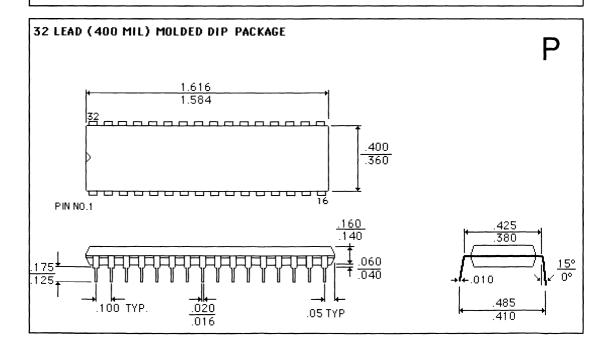

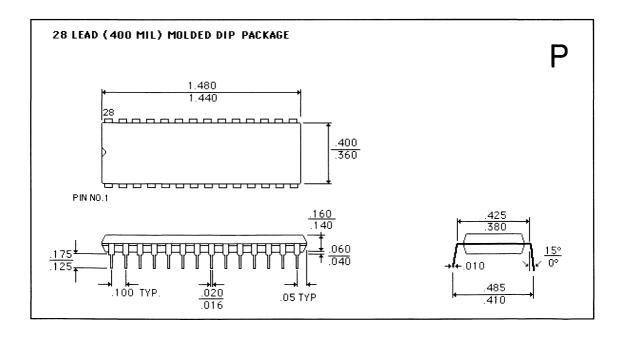

P = 400 mil Plastic DIP

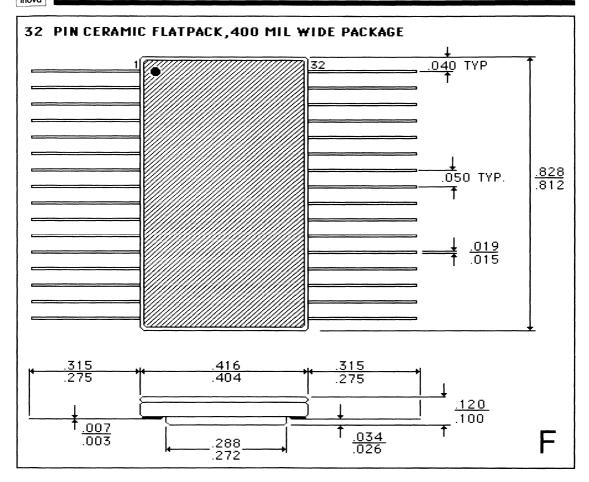

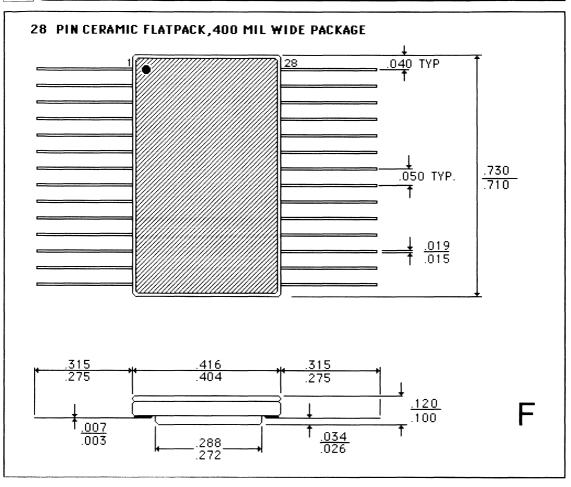

F = Flatpack

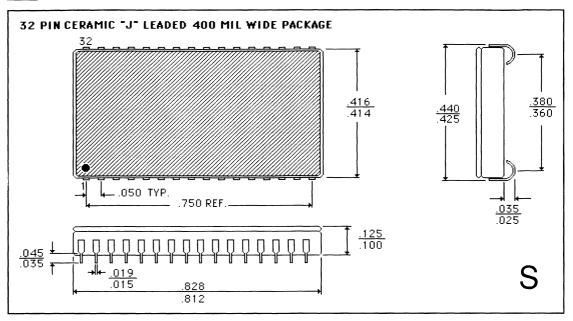

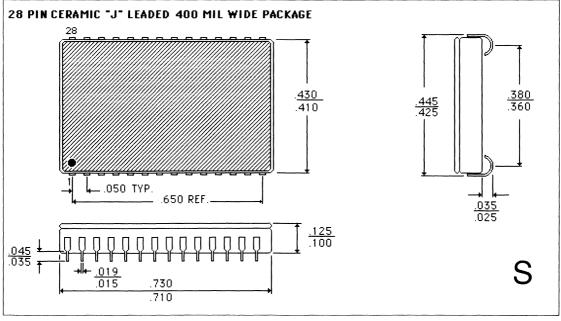

S = Ceramic SOJ

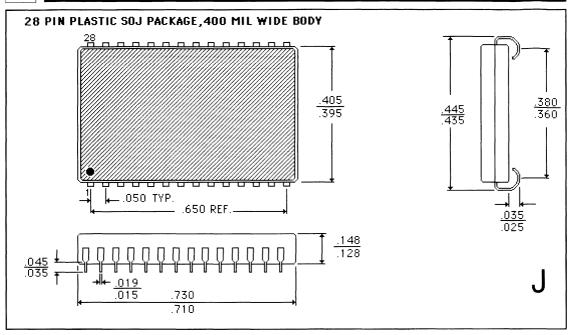

J = Plastic SOJ

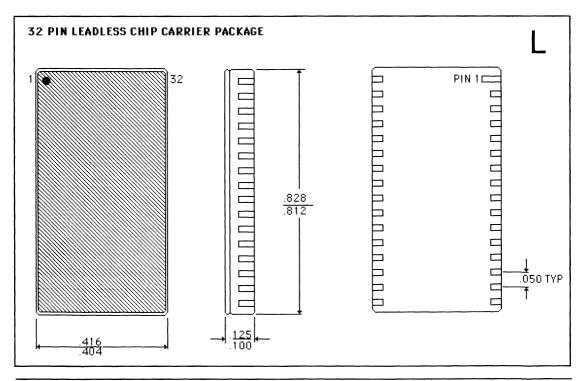

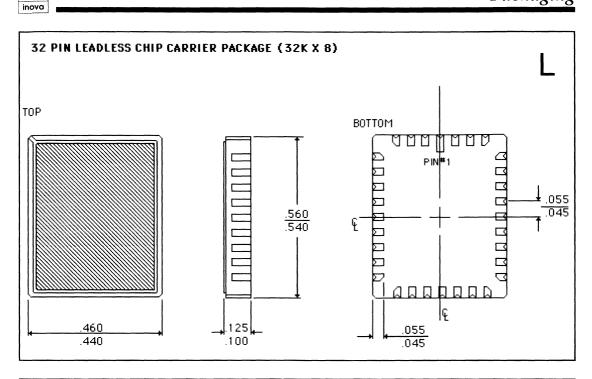

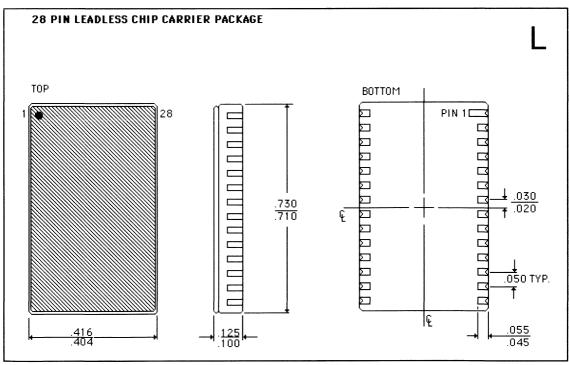

L = Leadless Chip Carrier

G = Pin Grid Array

### **Product Selector Guide**

# 128K x 8 bit SRAMs

| Inova       | Access Time | Packag        | es   | Temp    |                       |      |

|-------------|-------------|---------------|------|---------|-----------------------|------|

| Part Number | ns Max      | Type          | Pins | Range   | Comments              | Page |

| S128K8      | 25, 35, 45  | C, D, E, T, F | 32   | C, I, M | 25 ns commercial only |      |

|             | 55, 70, 85  | S, L, J, P    |      |         |                       | 49   |

|             | 100, 120    |               |      |         |                       |      |

| S128K8L     | 25, 35, 45, | C, D, E, T, F | 32   | C, I, M | DESC SMD No.          |      |

|             | 55, 70, 85  | S, L, J, P    |      |         | 5962-89598            | 49   |

|             | 100, 120    |               |      |         | 25 ns commercial only |      |

| S128K8T     | 25, 35, 45, | C, D, E, T, F | 32   | C, I, M | 25 ns commercial only |      |

|             | 55, 70, 85  | S, L, J, P    |      |         |                       | 57   |

|             | 100, 120    |               |      |         |                       |      |

| S128K8TL    | 25, 35, 45, | C, D, E, T, F | 32   | C, I, M | 25 ns commercial only |      |

|             | 55, 70, 85  | S, L, J, P    |      |         |                       | 57   |

|             | 100, 120    |               |      |         |                       |      |

C = Commercial Temperature Range (0°C to 70°C)

I = Industrial Temperature Range (-40°C to 85°C)

M = Military Temperature Range (-55°C to 125°C)

L suffix on base part number = Low Power Device

T suffix on base part number = Two Chip Select Option

C = 600 mil Ceramic Sidebrazed DIP

D = 400 mil CERDIP

E = 400 mil Ceramic Sidebrazed DIP

T = 300 mil Ceramic Sidebrazed DIP

P = 400 mil Plastic DIP

F = Flatpack

S = Ceramic SOJ

J = Plastic SOJ

L = Leadless Chip Carrier

G = Pin Grid Array

# 64K x 16 bit SRAMs

| Inova       | Access Time  | Packag | es   | Temp    |              |      |

|-------------|--------------|--------|------|---------|--------------|------|

| Part Number | ns Max       | Type   | Pins | Range   | Comments     | Page |

| S64K16      | 45, 55, 70,  | С      | 40   | C, I, M | DESC SMD No. | 65   |

|             | 85, 100, 120 |        |      |         | 5962-90858   |      |

| S64K16L     | 45, 55, 70,  | С      | 40   | C, I, M | DESC SMD No. | 65   |

|             | 85, 100, 120 |        |      |         | 5962-90858   |      |

# 256K x 4 bit SRAMs

| Inova       | Access Time | Packago                  | es   | Temp    |             |      |

|-------------|-------------|--------------------------|------|---------|-------------|------|

| Part Number | ns Max      | Type                     | Pins | Range   | Comments    | Page |

| S256K4      | 25, 35, 45  | C, E, P, F, S<br>J, L, T | 28   | C, I, M | Preliminary | 71   |

| S256K4L     | 25, 35, 45  | C, E, P, F, S<br>J, L, T | 28   | COM     | Preliminary | 71   |

# 1,024K x 1 bit SRAMs

| Inova       | Access Time | Packag                   | es   | Temp    |             |      |

|-------------|-------------|--------------------------|------|---------|-------------|------|

| Part Number | ns Max      | Type                     | Pins | Range   | Comments    | Page |

| S1M1        | 25, 35, 45  | C, E, P, F, S<br>J, L, T | 28   | C, I, M | Preliminary | 79   |

| S1M1L       | 25, 35, 45  | C, E, P, F, S<br>J, L, T | 28   | C, I, M | Preliminary | 79   |

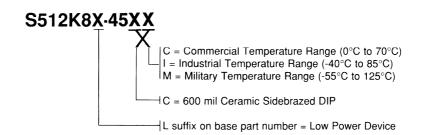

# 512K x 8 bit SRAMs

| Inova       | Access Time | Packago | es   | Temp    |             |      |

|-------------|-------------|---------|------|---------|-------------|------|

| Part Number | ns Max      | Type    | Pins | Range   | Comments    | Page |

| S512K8      | 45, 55, 70  | С       | 32   | C, I, M | Preliminary | 87   |

| S512K8L     | 45, 55, 70  | С       | 32   | C, I, M | Preliminary | 87   |

# 256K x 16 bit SRAMs

| Inova       | Access Time | Packag | es   | Temp    |                     |      |

|-------------|-------------|--------|------|---------|---------------------|------|

| Part Number | ns Max      | Type   | Pins | Range   | Comments            | Page |

| S256K16     | 55, 70, 85, | С      | 48   | C, I, M | Advance Information | 93   |

|             | 100, 120    |        |      |         |                     |      |

| S256K16L    | 55, 70, 85, | С      | 48   | C, I, M | Advance Information | 93   |

|             | 100, 120    |        |      |         |                     |      |

C = Commercial Temperature Range (0°C to 70°C)

I = Industrial Temperature Range (-40°C to 85°C) M = Military Temperature Range (-55°C to 125°C)

L suffix on base part number = Low Power Device

T suffix on base part number = Two Chip Select Option

C = 600 mil Ceramic Sidebrazed DIP

D = 400 mil CERDIP

E = 400 mil Ceramic Sidebrazed DIP

T = 300 mil Ceramic Sidebrazed DIP

P = 400 mil Plastic DIP

F = Flatpack

S = Ceramic SOJ

J = Plastic SOJ

L = Leadless Chip Carrier

G = Pin Grid Array

| inava miaraalaatra | onics corporation | 2220 Martin Avr | onuo Santa Clar | CA 05050    |  |

|--------------------|-------------------|-----------------|-----------------|-------------|--|

| inova microelectro | Phone: 408-980    | -0730 Fax: 408  | -980-1805       | a, CA 95050 |  |

|                    |                   |                 |                 |             |  |

|                    |                   |                 |                 |             |  |

# **Cross References**

# Cross Reference

| 32K x 8                                                                                                   |                                     | 32K x 8                                                                              |                                                  | 128K X 8                                                                                                              |                                      |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                                                                                                           | 55 nS                               | 1                                                                                    | 00 nS                                            | 70                                                                                                                    | d ns                                 |

| Competition<br>CY7C198<br>CY7C199<br>IDT71256S<br>IDT7M856<br>SRM22256C<br>KM68257<br>CXK58258<br>LH52256 | <b>Inova</b><br>S32K8-55<br>(p. 43) | Competition MB84256A GM76C256 CDM62256 HM62256 HY63C256 SRM20256C LC36256L CXK58257P | <b>Inova</b><br>S32K8-100<br>(p. 43)             | Competition<br>EDI8M8128<br>EDI88128<br>CXK581001<br>DPS128M8<br>HM628128<br>MSM8128<br>IDT8M824                      | <b>Inova</b><br>S128K8-70<br>(p. 49) |

|                                                                                                           | <b>9</b> 0 0                        | UM62256                                                                              |                                                  | EDI88130                                                                                                              | S128K8T-70<br>(p.57)                 |

| Competition                                                                                               | 70 nS<br>Inova                      | 128K X 8                                                                             |                                                  | 86                                                                                                                    | ā nS                                 |

| CXK58257SP<br>IDT71256S<br>IDT7M856<br>M5M5256A<br>SRM22256C                                              | S32K8-70<br>(p. 43)                 |                                                                                      | 5 nS<br><b>Inova</b><br>S128K8-25                | Competition<br>CXK581001<br>DPS128M8<br>EDI88128<br>M5M51008                                                          | <b>Inova</b><br>S128K8-85<br>(p. 49) |

| LH52256<br>DPS92256<br>EDI8832C                                                                           |                                     | Competition CXK581020                                                                | (p. 49)  5 nS  Inova  S128K8-35                  | SRM20100<br>MSM8128<br>HM658128<br>HM628128                                                                           |                                      |

| Competition                                                                                               | 85 mS<br>Inova                      | MT5C1008<br>DPS41288                                                                 | (p. 49)                                          | IDT8M824<br>EDI88130                                                                                                  | S128K8T<br>(p. 57)                   |

| HM62256<br>CXK58257M<br>SSI62256CD<br>IDT71256S<br>IDT7M856<br>GM76C256L<br>EDH8832C<br>EDI8832C          | S32K8-85<br>(p. 43)                 | Competition<br>CXK581020<br>MSM8128                                                  | Inova S128K8-45 (p. 49)  Inova S128K8-55 (p. 49) | Competition<br>EDI88128<br>HM658128<br>MSM8128<br>CXK581000<br>SRM20100<br>M5M51008<br>MS88128<br>MS12808<br>IDT8M824 | © nS Inova S128K8-100 (p. 49)        |

| 10                                                                                                        |                                     |                                                                                      |                                                  | EDI88130                                                                                                              | S128K8T-100<br>(p. 57)               |

# Cross Reference

| 128K X 8             |                           | 256K x 4             |           | 1M X 1                |                           |

|----------------------|---------------------------|----------------------|-----------|-----------------------|---------------------------|

| 120                  | ns                        |                      | 25 nS     | 25 nS                 |                           |

| Competition          | Inova                     | Competition          | Inova     | Competition           | Inova                     |

| <b>D</b> PS128M8     | S128K8-120                | 431004               | S256K4-25 | M5M51001              | S1M1-25                   |

| EDI8M8128            | (p. 49)                   | M5M51004             | (p. 71)   | MT5C1001              | (p. 79)                   |

| EDI88128             |                           | MT5C1005             |           | 431001                |                           |

| HM658128<br>MS12808  |                           | CYM1240<br>EDI8M4257 |           |                       |                           |

| CXK581000            |                           | EDIOW4237            |           | 35                    | nS                        |

| M5M51008             |                           |                      | 35 nS     | Competition           | Inova                     |

| MSM8128              |                           | Competition          | Inova     | M5M51001              | S1M1-35                   |

|                      |                           | EDI84256             | S256K4-35 | MT5C1001              | (p. 79)                   |

| EDI88130             | S128K8T-120               | EDI8M4257            | (p. 71)   | EDI811024             |                           |

|                      | (p. 57)                   | M5M51004             |           |                       |                           |

|                      |                           | MT5C1005             |           |                       | _                         |

| 64K x 16             |                           | HM624256             |           |                       | nS                        |

|                      |                           | VT624256             |           | Competition           | <b>Inova</b><br>S1M1-45   |

| 45                   | nS                        | IDT7M4042            |           | M5M51001<br>EDI811024 | 511vi1-45<br>(p. 79)      |

| Competition          | Inova                     |                      | 45 nS     | MSM11000              | (p. 73)                   |

| IDT8M624             | S64K16-45                 | Competition          | Inova     | WOWN TOO              |                           |

| DPS8M624             | (p.65)                    | MSM4256              | S256K4-45 |                       |                           |

| 55                   | m @                       | M5M51004             | (p. 71)   |                       |                           |

| Competition          | Inova                     | HM624256             |           | 512K x 8              |                           |

| EDH816H64            | S64K16-55                 | VT624256             |           |                       |                           |

| EDI8M1664            | (p.65)                    | EDI84256             |           | 45                    | nS                        |

| DPS8M624             | ,                         | EDI8M4257            |           | Competition           | Inova                     |

| IDT8M624             |                           | IDT7M4042            |           | CYM1464               | S512K8-45                 |

|                      |                           |                      |           | IDT7MB4048            | (p. 87)                   |

| 70                   |                           |                      |           | 57.0                  |                           |

| Competition          | <b>Inova</b><br>S64K16-70 |                      |           | Competition           | nS                        |

| EDH816H64<br>CYM1623 | 564K16-70<br>(p.65)       |                      |           | DPS512X8              | <b>Inova</b><br>S512K8-70 |

| DPS8M624             | (μ.υσ)                    |                      |           | IDT7M4048             | (p. 87)                   |

| DI GOMOZA            |                           |                      |           | 15171111010           | (ρ. στ)                   |

| 100                  | nS                        |                      |           |                       |                           |

| Competition          | inova                     |                      |           | 256K x 16             |                           |

| EDH816H64            | S64K16-100                |                      |           |                       |                           |

| EDI8F1664            | (p.65)                    |                      |           | 55,                   | 70 nS                     |

| DPS8M624             |                           |                      |           | Competition           | Inova                     |

|                      |                           |                      |           | EDI8M16256            | S256K16                   |

|                      |                           |                      |           |                       | (p. 93)                   |

| inova microelectronics corporation, 2220 Martin Avenue, Santa Clara, CA 95050 |  |

|-------------------------------------------------------------------------------|--|

| Phone: 408-980-0730 Fax: 408-980-1805                                         |  |

|                                                                               |  |

|                                                                               |  |

# Quality and Reliability

| inova microelectronics corporation, 2220 Martin Avenue, Santa Clara, CA 95050 |

|-------------------------------------------------------------------------------|

| Phone: 408-980-0730 Fax: 408-980-1805                                         |

|                                                                               |

|                                                                               |

# QUALITY & RELIABILITY OUR COMMITMENT TO SUPERIOR PRODUCT QUALITY

**Inova** is committed to excellence in product quality and reliability. Stringent controls are in place in all phases of product design and throughout manufacturing to achieve our goals. However, the only <u>true</u> measurement of that commitment is our customer's satisfaction. Our customers are our most important "Quality Monitor" and **Inova** is most responsive to their inputs.

There are six critical factors that are essential for **Inova** to achieve excellence in Quality and Reliability. They are:

- 1. A deep understanding of our customers' needs and wants that translates into useful products.

- 2. Long lasting relationships with customers going beyond the delivery of the product to include sales, service, and ease of use.

- 3. Close partnerships with suppliers and customers who feed suggestions for improvements back into our operations.

- 4. A commitment that runs from the top to the bottom of the organization to continuously improve the yield, quality, and reliability of our products.

- 5. A system for measuring these improvements accurately.

- 6. A focus on prevention of mistakes rather than correcting them.

A description of the systems and controls in place at **Inova** which assure that the highest quality parts are consistently supplied and that these parts have the highest reliability achievable follows. We are always happy to explain our quality and reliability programs in more detail in person.

## **QUALITY ASSURANCE METHODS**

#### **CUSTOMER INFORMATION**

**Inova Microelectronics Corporation** exists to satisfy customers' needs with high performance, high density semiconductor products. To succeed in this endeavor, our sales and marketing team must understand our customers thoroughly and communicate our customers' needs back to our organization effectively.

Once a customer's need is identified and can be solved by **Inova**, a product purchase is normally transacted. **Inova**'s commitment as a result of this purchase order does not terminate with the delivery of the product, but includes technical service and a healthy exchange of information to ensure that the device is easy for the customer to use. Suggestions from our customers on ways to improve our products, systems, and services are actively solicited from the entire **Inova** organization.

The quality of our organization is measured not only by the acceptability of our products, but by how our entire organization responds to our customers' needs.

#### **CUSTOMER-SPECIFIC DRAWINGS**

Drawings and specifications received from customers and agreed to by **Inova** are controlled by the marketing department. When revisions occur they are reviewed and agreed to as if they were new specifications. Inova generates an internal specification that is used to manufacture any product that is not "standard". The Quality department controls these customer specifications. While **Inova** encourages standardization and makes every effort to create a device that will satisfy the majority of customer needs, we do realize that customer requirements sometimes do not match our datasheet parts.

#### SUPPLIER COMMUNICATIONS

Potential suppliers are initially evaluated by Inova engineering and quality assurance departments to determine the viability of the supplier. Once the supplier is deemed viable by passing an exhaustive technical analysis, he is added to the Inova Approved Suppliers list. This list is maintained by both Engineering and Quality and only those suppliers on the list are used.

Inova controls are imposed on all our raw material suppliers. Procurement specifications are written

## Quality Assurance

to cover our requirements. These specifications are always referenced in the purchase orders placed with our suppliers and a copy is attached for reference.

**Inova** suppliers enjoy the same type of continuous communications that we strive to maintain with our customers. This constant dialogue ensures that timely improvements are made in both organizations to maximize the useful benefits of our customer/supplier relationships.

#### YIELD IMPROVEMENT

**Inova** is driven by constant yield improvement. Since there are a set number of die sites on a silicon wafer, **Inova's** goal is to continually drive process and design improvements to achieve the highest percentage of die sites producing good product. There is no higher priority in the product engineering department. Achieving high yields has a direct effect on the "cost of quality".

**Inova** spends a large proportion of its resources on yield improvement as a preventive measure in quality, rather than on inspection and rework as an inspection and failure detection measure. This constant perfecting of the product during the course of its lifetime assures a better part in terms of quality, reliability and costs as time goes by. This is the classic microelectronic "learning curve". Because of **Inova**'s proprietary Inroute<sup>TM</sup> technology, this objective is realized much earlier in **Inova**'s product life cycle.

#### DOCUMENTATION AND CONTROL OF MANUFACTURING

**Inova Quality Assurance** maintains a documentation system which covers the design, wafer fabrication, assembly, test, quality assurance, reliability, and marketing areas of our company. Device schematics & drawings for all piece parts are under document control. All materials used in the manufacture of **Inova** products are covered by material specifications. Sign-off approvals for all standard product manufacturing and procurement specifications are pre-defined and only approved specifications are used for procurement and production.

Original customer drawings are kept on file by **Inova** Marketing. When a customer's need can best be met by a special version of an **Inova** device, the customer's requirements are translated into a unique **Inova** internal specification that describes exactly how the part is built, tested and marked. This internal document eliminates any misunderstandings that may be introduced by directly using customer specifications.

## Quality Assurance

A revision control system is in effect for all schematics, drawings, and materials specifications. Each revision of a specification has an effectivity date and copies of all past revisions are kept on file and traceable.

#### PRODUCT CHANGE CONTROL

Changes to the design, materials, or process of an **Inova** product are thoroughly evaluated and qualified before being implemented. Product characterization and reliability tests are performed based on the type of change made.

Changes that affect device operation or interchangeability are communicated to customers with sufficient time to allow for the customer's evaluation and acceptance.

Changes to Military products are communicated to the qualifying activity.

#### IN-PROCESS MONITORS AND INSPECTIONS

While the basic philosophy at **Inova** is to "Do it right the first time", constant vigilance is required to verify the quality of our products and procedures. An extensive system of monitors and inspections are performed in the manufacturing and testing of our products. Information from these inspections is summarized for the management of the respective areas and for the general management team and corrective action is implemented when required to improve performance. To emphasize the importance of quality to the overall success of the company, quality measurement is used as one of the criteria in the assessment of **Inova** management's performance.

Because of our commitment to produce the most reliable product available for commercial, industrial and military OEMs, many of the inspection procedures for **Inova** product are based on MIL-STD-883, Revision C. We have found it easier and more cost effective to implement the most stringent military standards required for our devices and reap the benefits of those higher standards in our commercial products.

#### INCOMING INSPECTION OF PURCHASED MATERIALS

All materials purchased for use in the manufacture of **Inova** products are inspected before their actual use. Only approved and accepted product is used in production. Material that is rejected is returned to the vendor for corrective action.

**Inova** encourages partnership arrangements and open dialogue with all suppliers of **Inova** raw materials. Swift resolution of problems and the highest levels of quality are sought with all suppliers. **Inova** vendors are measured by their failure rate and willingness to solve problems should they occur. Excessive failures or a lack of cooperation leads to a vendor disqualification.

#### STATISTICAL PROCESS CONTROL

Statistical Process Control, or SPC, is a system of defect prevention through the application of statistical tools. These tools are used on data taken at critical process points in the manufacturing flow and provide insight into the manufacturing process itself. When the results are interpreted correctly, SPC provides opportunities for improvement in the overall manufacturing process. By the proper application of SPC, process variation is reduced and a more consistent and reliable product is manufactured.

**Inova** uses extensive SPC techniques in the analysis of wafer fabrication, assembly and test process parameters. All **Inova** manufacturing operations have SPC systems in place. Diffusion, implant, masking, gate oxidation, die attach, & wire bonding are just a few examples of manufacturing process points monitored.

#### **AUDIT AND CORRECTIVE ACTION**

In order to verify compliance to requirements, audits of all **Inova** manufacturing and quality control areas are carried out at least once per year. These audits are conducted by the Quality Assurance organization and records of each audit are kept on file. All discrepancies found on the audit result in a corrective action request. All corrective actions must be implemented and approved by the auditor before they are closed out. Pre-defined checklists are used for all audits and they are kept under document control.

#### TRAINING AND CERTIFICATION

All critical processes and inspections are performed by personnel who have been trained to perform their task in accordance with **Inova** requirements. Each person is trained and tested by a qualified individual to assure proficiency at the task. Individuals are retested periodically to verify proficiency.

#### **CALIBRATION**

All equipment used for measuring and testing of product is calibrated on an assigned schedule utilizing equipment and standards traceable to the National Bureau of Standards. The Quality Assurance group maintains the calibration of measuring equipment.

The calibration system is set up to comply with MIL-STD-45662. All manufactured products are measured and/or tested by equipment that has been properly calibrated on pre-defined schedule. Automatic testers, temperature forcing units, dimensional measurement tools, and electronic instruments of all types are examples of the types of equipment that **Inova** calibrates and maintains.

## **ELECTROSTATIC DISCHARGE (ESD) PREVENTION**

**Inova** has a complete electrostatic discharge (ESD) prevention program to prevent any ESD damage from occurring during the manufacturing process. This system is in full conformance with JEDEC Publication No. 108-A. Ground straps, grounded table tops, smocks, and grounded equipment are all utilized. All personnel are trained to prevent ESD damage. Parts are packed for shipment in ESD protective packaging. All ESD safeguards are checked periodically to verify grounds and connections.

All **Inova** devices are designed with protection networks on inputs and outputs to assure adequate protection from normal ESD damage. New designs are thoroughly tested prior to release to assure sufficient levels of ESD protection. ESD acceptance tests are conducted per MIL-STD-883C, method 3015.

Quality Assurance

### **CUSTOMER RETURNS & FAILURE ANALYSIS**

Even using the most extensive quality assurance and reliability techniques, product failures may occur in the field. Field failures are given the highest priority for failure analysis and feedback. **Inova** parts which are returned are analyzed to determine the root cause of the problem. All failure analysis information is communicated directly to the customer by **Inova**. If changes are made by **Inova** to the testing or the manufacturing flow of a product to correct a problem then the effective date code of the change is also communicated to the customer.

**Inova** maintains a state-of-the-art failure analysis lab. Our failure analysis equipment includes a Scanning Electron Microscope (SEM), a Wafer Parametric Tester, and various electronic failure verification and fault isolation tools. All quality conformance and field failures are thoroughly analyzed to determine the cause of the failure and corrective action. Yield-related failures are analyzed to determine actions neccessary to improve manufacturing yields. An in-depth failure analysis is essential to improve the yield, quality and reliability of **Inova** products.

#### SUMMARY

**Inova** is committed to supplying the highest quality, most reliable semiconductor products available in the industry. We strive to solve our customers need with our products and our people, but can be most successful if we maintain a high level of communication with you, our customer, and our suppliers.

If you have a suggestion to help improve any of our products or systems, please contact us. We definitely want to be your Number 1 supplier of semiconductor products.

Reliability

#### RELIABILITY

#### **DESIGN**

At **Inova**, building high quality, highly reliable microcircuits is no accident. We start with the product design itself. No reliability program can be successful without the design and process engineering team understanding exactly what the reliability goals of a particular design project are and what design and process considerations must be made to achieve those goals.

The wafer fab process is **Inova**'s first reliability consideration. The fabrication process must be fully characterized and proven using known test structures to measure individual device performance and reliability. Once the process parameters and the design rules are documented, the circuit designer can begin to design the microcircuit.

Other reliability considerations during the device design process include ESD protection networks and latch-up protection. **Inova** uses very conservative design margin simulations to assure that new products perform well within the specification limits.

The next area of concern in device design is the assembly of the finished good die. Packaging design rules are followed to assure that assembly manufacturing tolerances are observed.

**Inova** knows that to be competitive in the world market in the 1990's and beyond, we must design for optimum manufacturing capability. Inova designers work closely with production engineers to make sure that new designs are optimized for manufacturing. This is an extremely important consideration that produces dramatic benefits with new **Inova** products as they ramp up in production.

#### CHARACTERIZATION & QUALIFICATION TESTING

Once an **Inova** microcircuit is designed and produced, it must be characterized and qualified. The characterization of a new **Inova** design is extremely important to verify that the performance meets the design goals and the device specification. Three wafer fab lots are required for characterization to assure consistency of the process and design. Extensive tests are done at this stage to verify that the new product will meet all performance goals. Thorough characterization assures that **Inova** microcircuits will perform in all possible applications and under all conceivable conditions.

Qualification tests are done to verify the long term reliability of the device under all conceivable conditions. These tests are designed to accelerate failures whenever possible to allow for relatively short duration tests which can still accurately predict longer term failure rates. Reliability tests are

divided into "die related" tests and "package related" tests. The tests that **Inova** performs are described below:

### **PACKAGE RELATED TESTS**

|             |                           | SAMPLE | MAX %     |

|-------------|---------------------------|--------|-----------|

| TEST        | CONDITIONS                | SIZE   | FAIL*     |

| MARK        | MIL-STD-883C, Method 2015 | 4      | 0         |

| PERM        |                           |        |           |

| SOLDER-     | MIL-STD-883C, Method 2003 | 84     | LTPD = 10 |

| ABILITY     | (# OF LEADS TESTED)       |        |           |

| BOND        | MIL-STD-883C, Method 2011 | 60     | LTPD = 15 |

| STRENGTH    | (# OF LEADS TESTED)       |        |           |

| PHYSICAL    | MIL-STD-883C, Method 2016 | 15     | 0         |

| DIMENSIONS  |                           |        |           |

| LEAD        | MIL-STD-883C, Method 2004 | 15     | 0         |

| INTEGRITY   | Condition B2              |        |           |

| INTERNAL    | MIL-STD-883C, Method 1018 | 5      | 1/5       |

| WATER VAP.  | (<5000PPM)                |        |           |

| ADHESION OF | MIL-STD-883C, Method 2025 | 15     | 0         |

| LEAD FINISH |                           |        |           |

| LID TORQUE  | MIL-STD-883C, Method 2024 | 5      | 0         |

|             |                           |        |           |

<sup>\*</sup> Maximum percentage of failures allowed by MIL-STD-883C.

### **SERIES 1**

|            |                           | SAMPLE | MAX % |

|------------|---------------------------|--------|-------|

| TEST       | CONDITIONS                | SIZE   | FAIL* |

| THERMAL    | MIL-STD-883C, Method 1011 | 15     | 0     |

| SHOCK      | Condition B, 15 CYCLES    |        |       |

| TEMP CYCLE | MIL-STD-883C, Method 1010 | 15     | 0     |

| COND C,    | 100 CYCLES                |        |       |

| FINE/GROSS | MIL-STD-883C, Method 1014 | 15     | 0     |

| LEAK       |                           |        |       |

| VISUAL     | MIL-STD-883C              | 15     | 0     |

|            |                           |        |       |

| TEST       | PER DATA SHEET AT ROOM,   | 15     | 0     |

| ENDPOINT   | HOT, & COLD TEMP.         |        |       |

<sup>\*</sup> Maximum percentage of failures allowed by MIL-STD-883C.

## **DIE RELIABILITY TESTS**

|           |                       | SAMPLE | MAX % |

|-----------|-----------------------|--------|-------|

| TEST      | CONDITIONS            | SIZE   | FAIL* |

| INFANT    | 168 hours/125°C       | 100    | 1%    |

| MORTALITY | or equivalent         |        |       |

| LIFE      | 1000 hours/125°C      | 100    | 1%    |

| TEST      | or equivalent         |        |       |

| TEMP      | 100 CYCLES -65/+150°C | 50     | 2%    |

| CYCLE     |                       |        |       |

<sup>\*</sup> Maximum percentage of failures allowed by MIL-STD-883C.

#### **DIE PERFORMANCE TESTS**

|              |                                | SAMPLE | MIL     | INOVA   |

|--------------|--------------------------------|--------|---------|---------|

| TEST         | CONDITIONS                     | SIZE   | SPEC*   | SPEC    |

| ESD          | MIL-STD-883C, Method 3015      | 3      | > 1000V | > 2000V |

| SENSITIVITY  | (Human Body Model)             |        |         |         |

| LATCH-<br>UP | INOVA Specification<br>TE-0201 | 5      | 0       | 0       |

<sup>\*</sup> Maximum percentage of failures allowed by MIL-STD-883C.

These tests are performed on each new **Inova** design. Changes made to existing designs to improve performance or increase manufacturing yields are also requalified. Whenever a change is made, Inova analyzes it to determine its possible effect on device performance or reliability. All changes that may have an effect on device performance or reliability are recharacterized and requalified before they are put into production. Because some **Inova** customers require notification and requalification at their facility before a redesigned product may be supplied, **Inova** policy requires us to notify those customers well in advance of major changes in the design to allow time for requalification, if necessary.

#### **MILITARY PRODUCTS**

**Inova** is a major supplier of Military Static RAMs to the U.S. Government and to its prime and subcontractors. The ability to supply this level of high reliability product requires **Inova** to have the quality systems in place to meet the requirements of MIL-STD-883C, Paragraph 1.2.1, and the referenced paragraphs of MIL-M-38510.

In addition to these military specifications, **Inova** complies with other associated Quality System specifications, such as MIL-Q-9858A & MIL-I-45208A. **Inova** processes all military product through the screening flow of MIL-STD-883C, Method 5004, Class B. Quality Conformance Inspection (QCI) testing is performed per MIL-STD-883C, Method 5005, Class B. A description of **Inova**'s screening and QCI testing follows.

#### **SCREENING FLOW**

|                                | Inova Specification or            |

|--------------------------------|-----------------------------------|

| Requirement                    | MIL-STD-883C Test Method          |

| Internal Visual Inspection     | Method 2010, Condition B          |

| Temperature Cycling            | Method 1010, Condition C          |

|                                | (50 cycles)                       |

| Constant Acceleration          | Method 2001, Condition D, Y1 Only |

| External Visual Inspection     | Para. 3.2 of Method 1010          |

| Initial Electrical Test        | TE - 0202                         |

| Burn-in                        | Method 1015, Condition D          |

|                                | 80 Hrs @ 150° C.                  |

| Final Electrical Test (Note 1) | TE - 0202, 25° C                  |

|                                |                                   |

|                                | Inova Specification or  |

|--------------------------------|-------------------------|

| Requirement                    | MIL-STD-883 Test Method |

| Percent Defective Allowable    | < 3%                    |

| Final Electrical Test          | TE - 0202, +125°/-55°   |

| Mark                           | AS - 0402               |

| Group A Test @+125°/-55° C     | TE - 0202               |

| Hermeticity, Fine & Gross Leak | Method 1014             |

| Group A Test @ 25° C           | TE - 0202               |

| External Visual Examination    | QA - 0302               |

| Pack                           | QA - 0202               |

| Final QA                       | QA - 0201               |

| Ship                           | QA - 0202               |

|                                |                         |

Note 1: Parts must be tested @ 25° C within 96 hours of removal from burn-in.

#### **QUALITY CONFORMANCE TESTING**

Quality conformance testing follows the requirements contained in MIL-STD-883C, paragraph 1.2.1 (17). Group A and B tests are required on every inspection lot and Group C and D tests are done as required by MIL-M-38510.

# MIL-STD-883C and Inova Specifications

#### **GROUP A TESTS**

|             |                             | (ACC/SS) |

|-------------|-----------------------------|----------|

| TEST        | DESCRIPTION                 | OR LTPD  |

| Subgroup 1  | Static Tests @ +25° C.      | 0/116    |

| Subgroup 2  | Static Tests @ +125° C.     | 0/116    |

| Subgroup 3  | Static Tests @ -55° C.      | 0/116    |

| Subgroup 7  | Functional Tests @ +25° C.  | 0/116    |

| Subgroup 8A | Functional Tests @ +125° C. | 0/116    |

| Subgroup 8B | Functional Tests @ -55° C.  | 0/116    |

| Subgroup 9  | Switching Tests @ +25° C.   | 0/116    |

| Subgroup 10 | Switching Tests @ +125° C.  | 0/116    |

| Subgroup 11 | Switching Tests @ -55° C.   | 0/116    |

#### **GROUP B TESTS**

|            |                                                   | (ACC/SS) |

|------------|---------------------------------------------------|----------|

| TEST       | DESCRIPTION                                       | OR LTPD  |

| Subgroup 2 | Resistance to solvents, MIL-STD-883C, Method 2015 | 0/4      |

| Subgroup 3 | Solderability, MIL-STD-883C, Method 2003          | 10       |

| Subgroup 4 | Bond Strength, MIL-STD-883C, Method 2011, Cond. D | 10       |

# Reliability

**GROUP C TESTS**

|            |                                        | (ACC/SS) |

|------------|----------------------------------------|----------|

| TEST       | DESCRIPTION                            | OR LTPD  |

| Subgroup 1 | Steady State Life Test                 | 5        |

|            | MIL-STD-883C, Method 1005, Condition D |          |

|            | 184 hrs @ 150° C                       |          |

|            | End Point Electrical Parameters        | 5        |

|            | Subgroups 2, 3, 7, & 8                 |          |

#### **GROUP D TESTS**

|            |                                                      | (ACC/SS) |

|------------|------------------------------------------------------|----------|

| TEST       | DESCRIPTION                                          | OR LTPD  |

| Subgroup 1 | Physical Dimensions, MIL-STD-883C,                   | 15       |

|            | Method 2016                                          |          |

| Subgroup 2 | Lead Integrity, MIL-STD-883C,                        | 15       |

|            | Method 2004, Condition B <sub>2</sub> (lead fatigue) |          |

| Subgroup 3 | Thermal Shock, MIL-STD-883C,                         | 15       |

|            | Method 1011, Condition B, 15 cycles                  |          |

|            | Temperature Cycling, MIL-STD-883C,                   | 15       |

|            | Method 1010, Condition C, 100 cycles                 |          |

|            | Moisture Resistance, MIL-STD-883C,                   | 15       |

|            | Method 1004                                          |          |

|            | Fine & Gross Leak Test, MIL-STD-883C,                | 15       |

|            | Method 1014                                          |          |

|            | Visual Inspection, MIL-STD-883C                      | 15       |

|            | End Point Electrical Parameters                      | 15       |

|            | Subgroups 2, 3, 7, & 8                               |          |

| Subgroup 4 | Mechanical Shock, MIL-STD-883C,                      | 15       |

|            | Method 2002, Condition B                             |          |

|            | Vibration, Variable Frequency, MIL-STD-883C,         | 15       |

|            | Method 2007, Condition A                             |          |

|            | Constant Acceleration, MIL-STD-883C,                 | 15       |

|            | Method 2001, Condition D (20KG),                     |          |

|            | $Y_1$ orientation                                    |          |

|            | Fine & Gross Leak Test, MIL-STD-883C,                | 15       |

|            | Method 1014                                          |          |

**GROUP D TESTS (cont'd)**

|                      |                                        | (ACC/SS) |

|----------------------|----------------------------------------|----------|

| TEST                 | DESCRIPTION                            | OR LTPD  |

| Subgroup 4, (cont'd) | Visual Inspection, MIL-STD-883C        | 15       |

|                      | End Point Electrical Parameters        | 15       |

|                      | Subgroups 2, 3, 7, & 8                 |          |

| Subgroup 5           | Salt Atmosphere, MIL-STD-883C,         | 0/15     |

|                      | Method 1009, Condition A               |          |

|                      | Visual Inspection, MIL-STD-883C        | 0/15     |

|                      | Fine & Gross Leak Test, MIL-STD-883C,  | 0/15     |

|                      | Method 1014                            |          |

| Subgroup 6           | Internal Water Vapor Content,          | 0/3      |

|                      | MIL-STD-883C, Method 1018, (< 5000ppm) |          |

| Subgroup 7           | Adhesion of Lead Finish,               | 0/15     |

|                      | MIL-STD-883C, Method 2025              |          |

| Subgroup 8           | Lid Torque, MIL-STD-883C,              | 0/5      |

|                      | Method 2024                            |          |

# 32K x 8 Static RAM

| Var. Davamatana                    |            | Dev               | rice Types        |              |      |

|------------------------------------|------------|-------------------|-------------------|--------------|------|

| Key Parameters<br>S32K8 and S32K8L | 55I<br>55C | 70M<br>70I<br>70C | 85M<br>85I<br>85C | 100M<br>100I | Unit |

| Access Time                        | 55         | 70                | 85                | 100          | nS   |

| Cycle Time                         | 55         | 70                | 85                | 100          | nS   |

| Output Enable Access               | 20         | 25                | 30                | 50           | nS   |

#### **Features**

- S32K8L is compliant to DESC Standardized Military Drawing 88552 (Standard power part compliant to 5962-88662)

- 2.0V Low-Power Data Retention Option (S32K8L)

- Military, industrial, and commercial temperature range

- Military grades compliant to MIL-STD-883C

- 28 pin JEDEC standard pinout

# General Description

The Inova S32K8 is a high performance 256K bit Static Random Access Memory (SRAM), organized as 32K eight bit bytes.

The S32K8 is manufactured using a highly reliable, four transistor cell CMOS process. This provides a component which combines low active and standby power characteristics with high performance.

All inputs and outputs are fully TTL compatible. Operation is fully static, so there is no need for extra control logic to generate clocks and timing strobes.

Every military grade device is fully compliant to MIL-STD-883C, paragraph 1.2.1. Industrial and commercial grade devices are produced in the same production line which ensures that they are also of the highest quality.

## **Package Options**

# Recommended Operating

**Conditions**

| Parameter            | Symbol            | Min. | Мах.           | Unit |

|----------------------|-------------------|------|----------------|------|

| Supply Voltage(1)    | V <sub>cc</sub>   | 4.5  | 5.5            | V    |

| Input HIGH Voltage   | V <sub>IH</sub>   | 2.2  | $V_{cc} + 0.5$ | V    |

| Input LOW Voltage    | V <sub>IL</sub>   | -0.5 | 0.8            | V    |

| Operating Temp. Mil. | T <sub>c</sub>    | -55  | 125            | °C   |

| Operating Temp. Ind. | T <sub>c</sub>    | -40  | 85             | °C   |

| Operating Temp. Comr | n. T <sub>c</sub> | 0    | 70             | °C   |

# **Absolute Maximum Ratings** (2)

| -55 °C to 125 °C                 |

|----------------------------------|

| -65 °C to 150 °C                 |

| -0.5V to 7.0 V                   |

| -0.5 V to V <sub>cc</sub> + 0.5V |

| 1 Watt                           |

| er Output 20 mA                  |

| ec) 260 °C                       |

|                                  |

#### Notes:

- 1. All voltages referenced to  $V_{ss}$  (GND).

- 2. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Truth Table**

| Mode              | <u>cs</u> | ŌĒ | WE | I/O<br>Operation | Supply<br>Current                 |

|-------------------|-----------|----|----|------------------|-----------------------------------|

| Standby           | H         | Χ  | Χ  | High Z           | I <sub>SB</sub> /I <sub>FSB</sub> |

| Read              | L         | L  | Н  | Output           | I <sub>CC2</sub>                  |

| Write             | L         | Χ  | L  | Input            | I <sub>CC2</sub>                  |

| Output<br>Disable | L         | Н  | Н  | High Z           | I <sub>CC2</sub>                  |

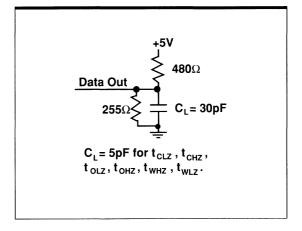

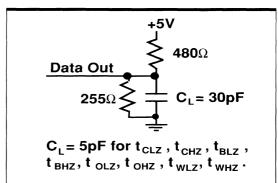

#### **Load Test Circuits**

# **Memory Scale**

| Access Time | 55  | 70  | 85  | 100 | Unit     |

|-------------|-----|-----|-----|-----|----------|

| S32K8       | 4.7 | 3.7 | 3.0 | 2.6 | kbits/ns |

# **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V |

|-------------------------------|-------------|

| Input Rise and Fall Times     | 5ns         |

| Input Timing Reference Levels | 1.5V        |

| Output Reference Levels       | 1.5V        |

#### **DC** and Operating Characteristics

M=Military; C=Commercial; I=Industrial

|                                               | Cumbal             | Total Conditions                                                                             |                | S3  | 2K8            |     | S32K8                 | L                   | ,,,,,,,,           |

|-----------------------------------------------|--------------------|----------------------------------------------------------------------------------------------|----------------|-----|----------------|-----|-----------------------|---------------------|--------------------|

| Parameters                                    | Symbol             | Test Conditions                                                                              |                | Min | Max            | Min | TYP<br>5V, 25 °C      | Max                 | UNITS              |

| Input Leakage                                 | 1461               | $V_{GG} = max, V_{IN} = GND \text{ to } V_{G}$                                               | C.             |     | 2              |     |                       | 2                   | μΑ                 |

| Output Leakage                                | Lo                 | $V_{OUT} = GND TO V_{CC} \cdot \overline{CS} \ge$                                            | V IH           |     | 2              |     |                       | 2                   | μА                 |

| Static Supply<br>Current                      | l <sub>CC1</sub>   | $\overline{CS} = V_{II}$ , $\overline{OE} = V_{IH}$<br>No Address Transitions                | C<br>I<br>M    |     | 80<br>85<br>90 |     | 55                    | 80<br>85<br>90      | mA                 |

| Dynamic Supply<br>Current                     | CC2                | $\overline{CS} \le V_{ii} \cdot \overline{OE} = V_{iii}$<br>Address Change every $t_{BC}$    | 70,85,100      |     | 110            |     | 95<br>90              | 110                 | mA                 |

| Standby Supply<br>Current with TTL<br>Inputs  | I<br>SB            | $\overline{\text{CS}} \geq \text{V}_{\text{IH}}$ Address Change every $\text{t}_{\text{RC}}$ | C<br>I<br>M    |     | 10<br>15<br>20 |     | 1.0                   | 1.5<br>2.0<br>3.0   | mA                 |

| Standby Supply<br>Current with<br>CMOS inputs | <br> FSB           | $\overline{\text{CS}} = \text{V}_{\text{cc}} \pm 0.2\text{V}$<br>No Address Transitions      | C<br>I<br>M    |     | 2<br>5<br>10   |     | 0.025                 | 0.75<br>1.25<br>2.5 | mA                 |

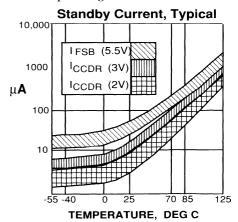

| Data Retention                                | I <sub>CCDR2</sub> | $\overline{CS} = V_{DR} \text{ min, } V_{CC} = 2.0V$                                         | / C<br>I<br>M  |     | NA<br>NA<br>NA |     | 5                     | 100<br>150<br>600   | μА                 |

| Current                                       | I <sub>CCDR3</sub> | $\overline{\text{CS}} = V_{DR} \text{ min, } V_{CC} = 3.0^{\circ}$                           | v C<br>I<br>M  |     | NA<br>NA<br>NA |     | 8                     | 150<br>225<br>900   | ,,,,               |

| Data Retention<br>Voltage                     | V <sub>DR</sub>    | V <sub>cc</sub> input voltage, minimu                                                        | m              | NA  |                | 2.0 |                       |                     | V                  |

| Output Low Voltage                            | V <sub>OL</sub>    | I <sub>OL</sub> = 8 mA                                                                       |                |     | 0.4            |     |                       | 0.4                 | V                  |

| Output High Voltage                           | V <sub>OH</sub>    | I <sub>OH</sub> = -4 mA                                                                      |                | 2.4 |                | 2.4 |                       |                     | V                  |

| Pin Capacitance                               |                    | Test Conditions                                                                              | Addresses      |     |                |     | CS. WE, OE            |                     | <b>Units</b><br>pF |

|                                               | V <sub>OH</sub>    | I <sub>OH</sub> = -4 mA                                                                      | Addresses<br>8 | 2.4 | Data I/0       |     | <i>CS</i> , <i>WE</i> |                     |                    |

#### AC Characteristics

(1)

|     |                                      | Ta                    | 55  | C,I | 70  | C,I,M | 85 ( | C, I, M | 100 | C,I,M | 120 | ) I,M |

|-----|--------------------------------------|-----------------------|-----|-----|-----|-------|------|---------|-----|-------|-----|-------|

| No. | Parameter                            | Symbol                | Min | Max | Min | Max   | Min  | Max     | Min | Max   | Min | Max   |

| 1   | Read Cycle Time                      | t <sub>RC</sub>       | 55  |     | 70  |       | 85   |         | 100 |       | 120 |       |

| 2   | Address Access Time                  | t AA                  |     | 55  |     | 70    |      | 85      |     | 100   |     | 120   |

| 3   | CS Access Time                       | t <sub>ACS</sub>      |     | 55  |     | 70    |      | 85      |     | 100   |     | 120   |

| 4   | Output Hold from Address Change      | t<br>OH               | 5   |     | 5   |       | 5    |         | 5   |       | 5   |       |

| 5   | CS Asserted to Output in Low Z       | t (0,2,0,3)           | 5   |     | 5   |       | 5    |         | 5   |       | 5   |       |

| 6   | CS Deasserted to Output in High Z    | t <sub>CHZ(2.3)</sub> | 0   | 35  | 0   | 35    | 0    | 35      | 0   | 35    | 0   | 35    |

| 7   | OE Asserted to Output Valid          | t <sub>OE</sub>       |     | 20  |     | 25    |      | 30      |     | 50    |     | 50    |

| 8   | OE Asserted to Output in Low Z       | t (01.Z(2.3)          | 0   |     | 0   |       | 0    |         | 0   |       | 0   |       |

| 9   | OE Asserted to Output in High Z      | t <sub>OHZ(2.3)</sub> | 0   | 35  | 0   | 35    | 0    | 35      | 0   | 35    | 0   | 35    |

| 10  | Write Cycle Time                     | t wc                  | 55  |     | 70  |       | 85   |         | 100 |       | 120 |       |

| 11  | Address Set-up Time                  | t <sub>AS</sub>       | 0   |     | 0   |       | 0    |         | 0   |       | 0   |       |

| 12  | Write Pulse Width                    | t <sub>wp</sub>       | 35  |     | 35  |       | 40   |         | 45  |       | 50  |       |

| 13  | Write Recovery Time                  | t wa                  | 5   |     | 5   |       | 5    |         | 5   |       | 5   |       |

| 14  | Data Hold Time                       | t <sub>DH</sub>       | 3   |     | 3   |       | 3    |         | 3   |       | 3   |       |

| 15  | Data Valid to End of Write           | t <sub>Dw</sub>       | 25  |     | 30  |       | 35   |         | 40  |       | 40  | i     |

| 16  | Output Active from End of Write      | t wt Z(2 3)           | 5   |     | 5   |       | 5    |         | 5   |       | 5   |       |

| 17  | WE Asserted to Output in High Z      | t <sub>whz(2.3)</sub> | 0   | 35  | 0   | 35    | 0    | 35      | 0   | 35    | 0   | 35    |

| 18  | Chip Deselect to Data Retention Time | t CDR(2)              | 0   |     | 0   |       | 0    |         | 0   |       | 0   |       |

| 19  | Operation Recovery Time              | t <sub>R(2)</sub>     |     | 55  |     | 70    |      | 85      |     | 100   |     | 120   |

| 20  | CS Asserted to End of Write          | t <sub>cw</sub>       | 45  |     | 60  |       | 75   |         | 75  |       | 75  |       |

| 21  | Address Valid to End of Write        | t AW                  | 45  |     | 60  |       | 75   |         | 75  |       | 75  |       |

Notes: (1) At Recommended Operating Conditions. All Values in Nanoseconds. (2) This Parameter is characterized initially and after any design or process change which could affect it. It is guaranteed to, but not tested to, the limits specified. (3) All I/O Transitions are measured ± 500mV from steady state with loading as specified in "Load Test Circuits."

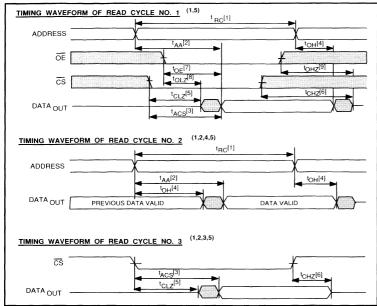

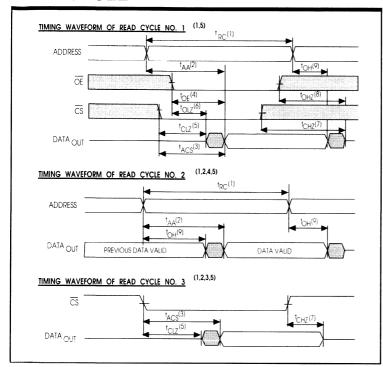

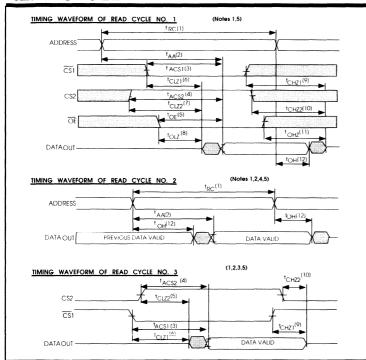

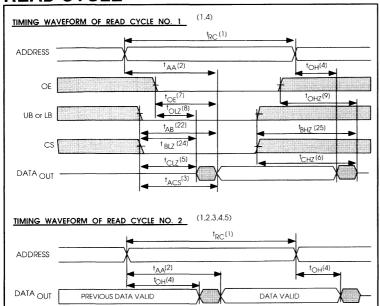

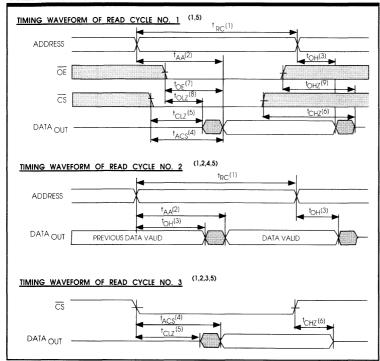

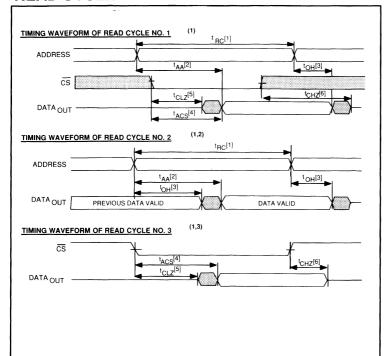

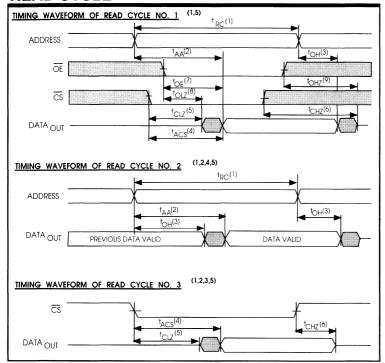

### **READ CYCLE**

Reading the device is accomplished by taking chip select  $(\overline{CS})$  and output enable(OE) LOW, while write enable (WE) remains inactive or high. Under these conditions, the contents of the memory location specified on the address pins will appear on the appropriate data input/output pins.

#### Notes:

- 1. WE is high for READ CYCLES.

- 2. Device is continuously selected,  $\overline{CS} = V_{IL}$  for all outputs active.

- 3. Address valid prior to or coincident with CS transition low.

- 4. OE =V.,

- 5. Data Output transitions measured ± 500mV from steady state. This parameter is sampled and not 100% tested

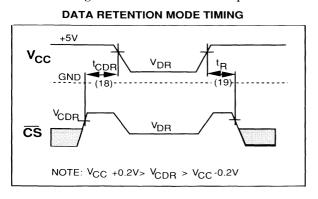

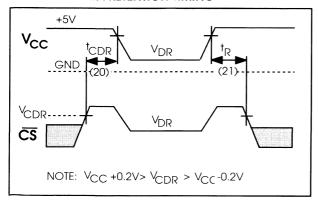

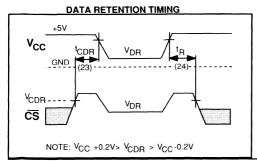

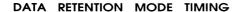

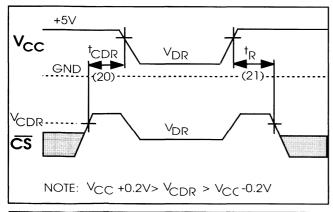

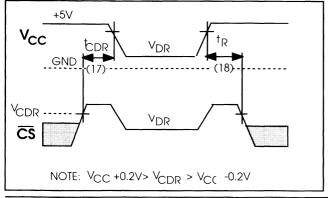

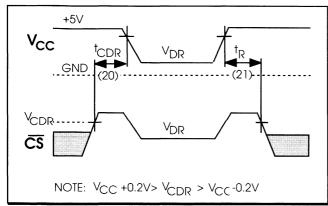

### Data Retention Cycle

S32K8 devices exhibit very low current drain when operated in Data Retention Mode. This Mode is entered by first driving Chip Select to  $V_{\rm CC}$  and subsequently driving both  $V_{\rm CC}$  and Chip Select to  $V_{\rm DR}$ . Chip Select must be set up before the V<sub>CC</sub> drops below its minimum level. When exiting from Data Retention Mode, the user must wait one full Read Cycle Time prior to asserting Chip Select.

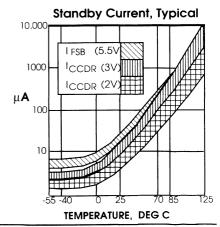

The curve showing typical device current is included to assist the user in understanding the relationship of the current required by the part when its Temperature and Voltage vary. The device is tested and guaranteed to conditions specified under DC and Operating Conditions.

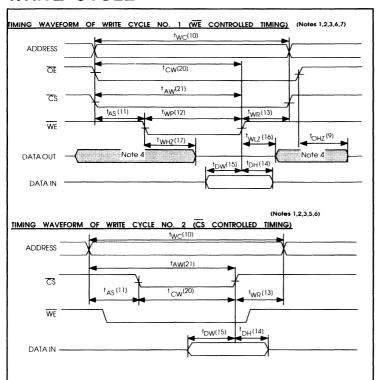

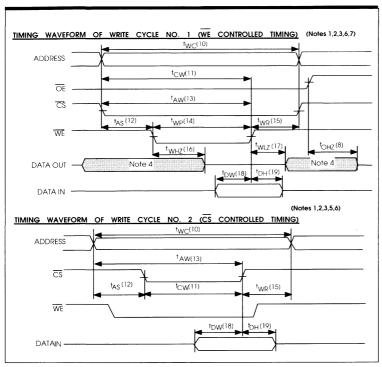

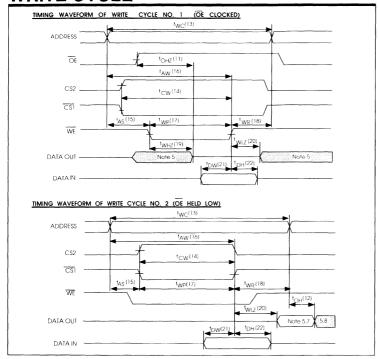

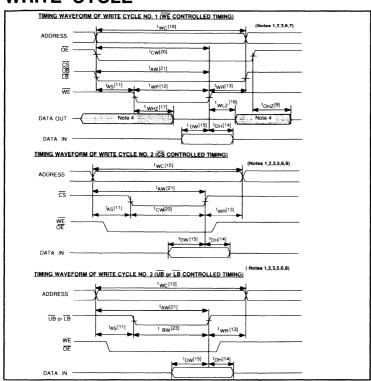

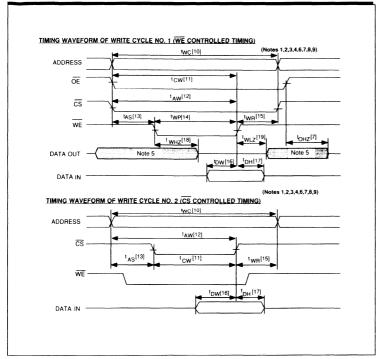

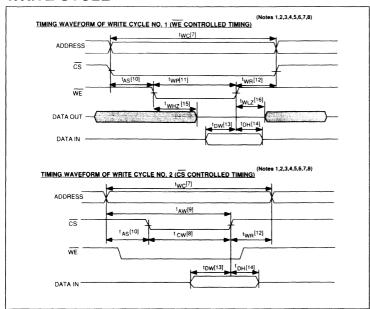

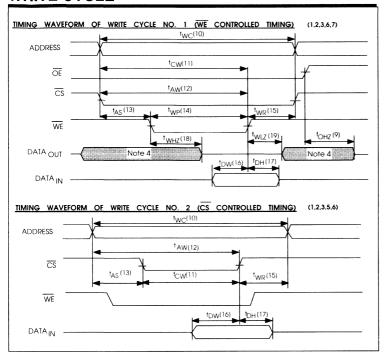

#### WRITE CYCLE

Writing to the S32K8 is achieved when the chip select (CS) and write enable (WE) inputs are LOW. Data on the input/output pins is written into the memory location specified on the address pins (A0-A14).

The input/output pins remain in a high impedance state when chip select (CS) or output enable (OE) is HIGH, or write enable (WE) is LOW.

#### **Notes:**

- 1.  $\overline{\text{WE}}$  or  $\overline{\text{CS}}$  must be high during all address transitions.

- 2. A write occurs during the overlap  $(t_{wp})$  of a low  $\overline{CS}$  and a low  $\overline{WE}$ .

- 3.  $t_{WR}$  is measured from the earlier of  $\overline{CS}$  or  $\overline{WE}$  going high to the end of the write cycle.

- 4. During this period, I/O pins are in the output state, and input signals must not be applied.

- 5. If the  $\overline{\text{CS}}$  low transitions occurs simultaneously with or after the  $\overline{\text{WE}}$  low transition, the outputs remain in a high impedance state.

- 6. Data output transitions are measured  $\pm$  500mV from steady state. This parameter is sampled and not 100% tested.

- 7. During a  $\overline{\text{WE}}$  controlled write cycle, write pulse low is  $\geq$  t<sub>DW</sub> + t<sub>WHZ</sub> to allow the I/O drivers to turn off and data to be placed on the the bus for the required TDW. If  $\overline{\text{OE}}$  is high during a  $\overline{\text{WE}}$  controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified TWP.

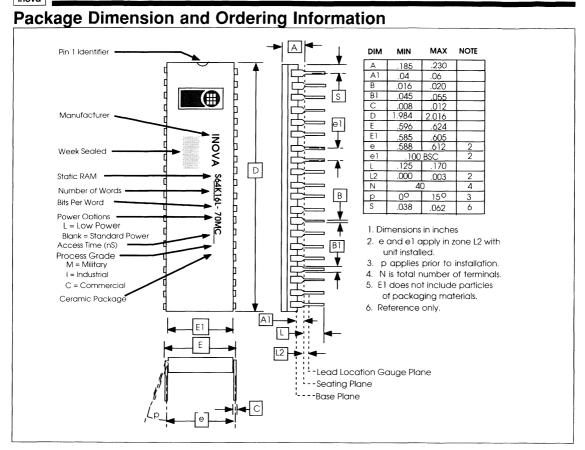

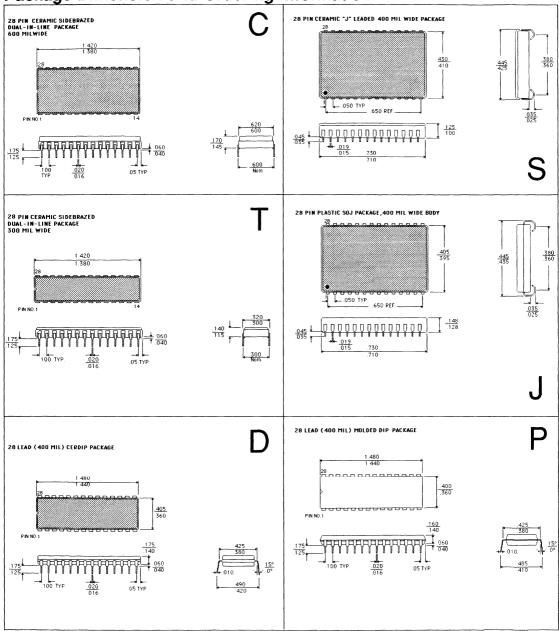

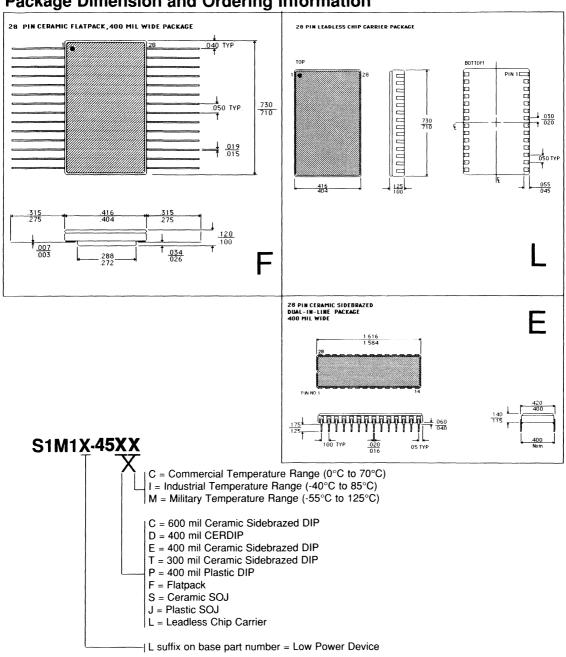

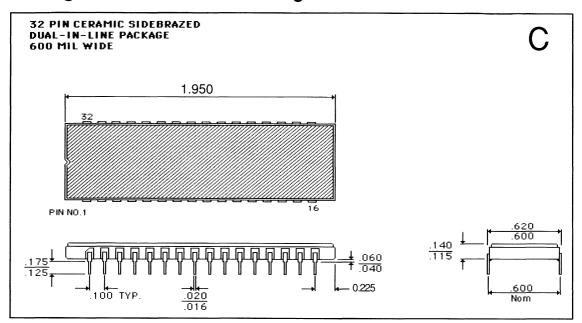

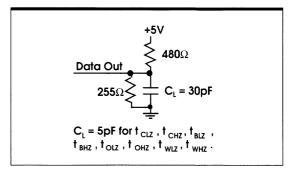

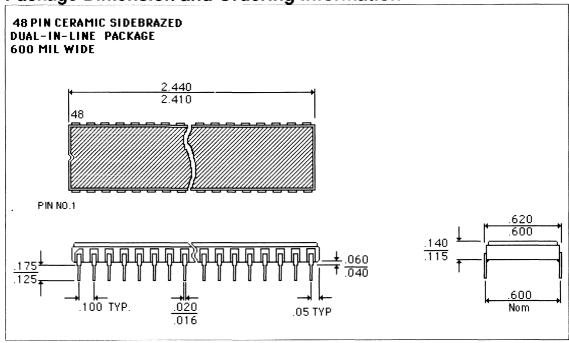

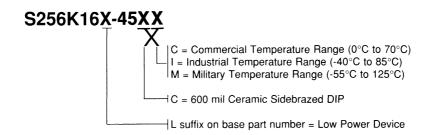

# **Package Dimension and Ordering Information**

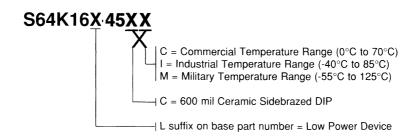

# C = Commercial Temperature Range (0°C to 70°C) I = Industrial Temperature Range (-40°C to 85°C) M = Military Temperature Range (-55°C to 125°C) C = 600 mil Ceramic Sidebrazed DIP L = Leadless Chip Carrier L suffix on base part number = Low Power Device

# 128K x 8 Static RAM

|                                      | Device Types |                   |                   |                   |                   |                   |                      |      |  |  |  |  |

|--------------------------------------|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|------|--|--|--|--|

| Key Parameters<br>S128K8 and S128K8L | 25C          | 35M<br>35I<br>35C | 45M<br>45I<br>45C | 55M<br>55I<br>55C | 70M<br>70I<br>70C | 85M<br>85I<br>85C | 100M<br>100I<br>100C | Unit |  |  |  |  |

| Access Time                          | 25           | 35                | 45                | 55                | 70                | 85                | 100                  | nS   |  |  |  |  |

| Cycle Time                           | 25           | 35                | 45                | 55                | 70                | 85                | 100                  | nS   |  |  |  |  |

| Output Enable Access                 | 10           | 15                | 15                | 20                | 25                | 30                | 50                   | nS   |  |  |  |  |

#### **Features**

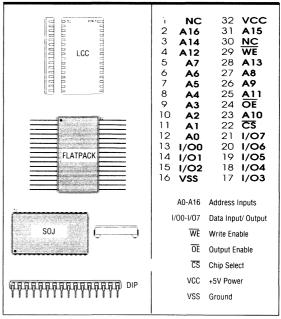

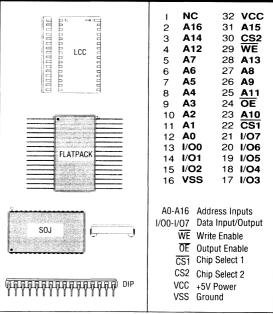

- 32 pin DIP, LCC, SOJ, Flatpack

- Advanced 4-T CMOS technology

- S128K8 is compliant to DESC Standardized Military Drawing No. 5962-89598

## **General Description**

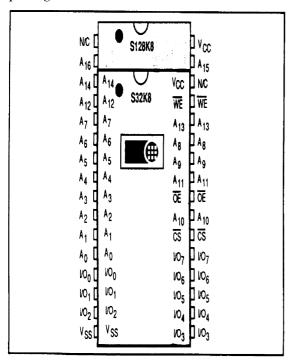

The Inova S128K8 is a high performance one megabit Static Random Access Memory (SRAM) organized as 128K eight -bit bytes.

The S128K8 is manufactured using a highly reliable, four transistor cell CMOS process. This provides a component which combines low active and standby power characteristics with high performance.

All inputs are fully TTL-compatible. Operation is fully static, without need for extra control logic to generate clock signals.

Every military grade device is fully compliant to MIL-STD-883C, paragraph 1.2.1. Industrial and commercial grade devices are fabricated in the same production line which assures that they are also of the highest quality.

- 300 mil DIP for 25, 35, 45 ns parts

- Military, industrial, and commercial temperature range

- Military grades compliant to MIL-STD-883C

# Package Options

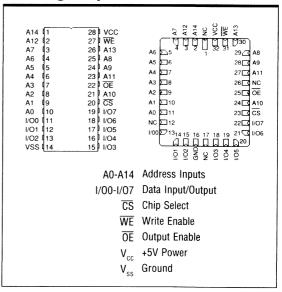

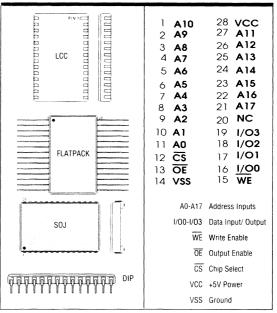

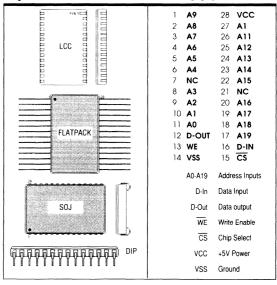

# **Pinout**

# **Recommended Operating**

**Conditions**

| Parameter            | Symbol            | Min. | Мах.                 | Unit |

|----------------------|-------------------|------|----------------------|------|

| Supply Voltage(1)    | V <sub>cc</sub>   | 4.5  | 5.5                  | V    |

| Input HIGH Voltage   | V <sub>IH</sub>   | 2.2  | V <sub>cc</sub> +0.5 | V    |

| Input LOW Voltage    | V <sub>II</sub>   | -0.5 | 0.8                  | V    |

| Operating Temp. Mil. | T <sub>c</sub>    | -55  | 125                  | °C   |

| Operating Temp. Ind. | T <sub>c</sub>    | -40  | 85                   | °C   |

| Operating Temp. Comr | n. T <sub>c</sub> | 0    | 70                   | °C   |

# Absolute Maximum Ratings (2)

| , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                            |

|-----------------------------------------|----------------------------|

| Temperature Under Bias                  | -55 °C to 125 °C           |

| Storage Temperature                     | -65 °C to 150 °C           |

| Supply Voltage <sup>(1)</sup>           | -0.5V to 7.0 V             |

| Signal Voltage On Any Pin               | -0.5 V to $V_{cc}$ + 0.5 V |

| Power Dissipation                       | 1 Watt                     |

| D.C. Continuous Output Current          | Per Output 20 mA           |

| Lead Temperature (Soldering 10          | sec) 260 °C                |

|                                         |                            |

#### Notes:

- 1. All voltages referenced to  $V_{ss}$  (GND).

- 2. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Truth Table**

| Mode              | <u>cs</u> | 0E | WE | I/O<br>Operation | Supply<br>Current                 |

|-------------------|-----------|----|----|------------------|-----------------------------------|

| Standby           | Н         | X  | X  | High Z           | I <sub>SB</sub> /I <sub>FSB</sub> |

| Read              | L         | L  | Н  | Output           | I <sub>CC2</sub>                  |

| Write             | L         | Χ  | L  | Input            | I <sub>CC2</sub>                  |

| Output<br>Disable | L         | Н  | Н  | High Z           | I <sub>CC2</sub>                  |

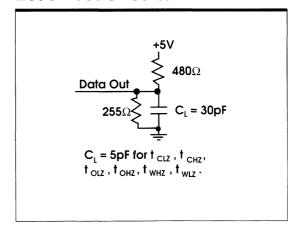

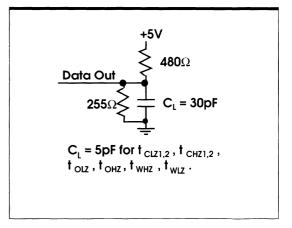

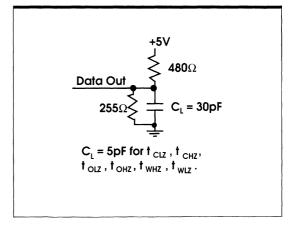

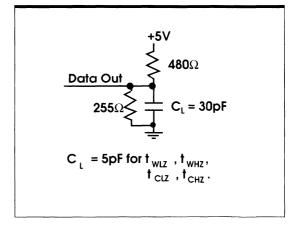

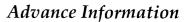

#### **Load Test Circuits**

# **Memory Scale**

| Access | Time | 25 | 35 | 45 | 55 | 70 | 85 | 100 | Unit     |

|--------|------|----|----|----|----|----|----|-----|----------|

| S12    | 8K8  | 40 | 29 | 22 | 18 | 14 | 11 | 10  | kbits/ns |

# **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V |

|-------------------------------|-------------|

| Input Rise and Fall Times     | 5ns         |

| Input Timing Reference Levels | 1.5V        |

| Output Reference Levels       | 1.5V        |

# **DC and Operating Characteristics** L=Low Power, S = Standard Power

| Symbol                |   | 2    | 5   | 3    | 5   | 4    | 5   | 5    | 5   | 7    | 0   | 8    | 5   | 10   | )0  | Units   |

|-----------------------|---|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|---------|

|                       |   | L    | S   | L    | S   | L    | S   | L    | S   | L    | S   | L    | S   | L    | S   |         |